全球首顆!復(fù)旦團隊研發(fā)二維-硅基混合架構(gòu)閃存芯片

關(guān)鍵詞: 二維-硅基混合架構(gòu)閃存芯片 長纓CY-01架構(gòu) 二維閃存技術(shù) CMOS工藝 芯片集成創(chuàng)新 復(fù)旦大學(xué)

時隔半年

繼“破曉(PoX)”皮秒閃存器件問世

復(fù)旦大學(xué)在二維電子器件工程化道路上

再獲里程碑式突破!

復(fù)旦大學(xué)集成芯片與系統(tǒng)全國重點實驗室

集成電路與微納電子創(chuàng)新學(xué)院

周鵬-劉春森團隊

研發(fā)的“長纓(CY-01)”架構(gòu)

將二維超快閃存器件“破曉(PoX)”

與成熟硅基CMOS工藝深度融合

率先研發(fā)出全球首顆

二維-硅基混合架構(gòu)芯片

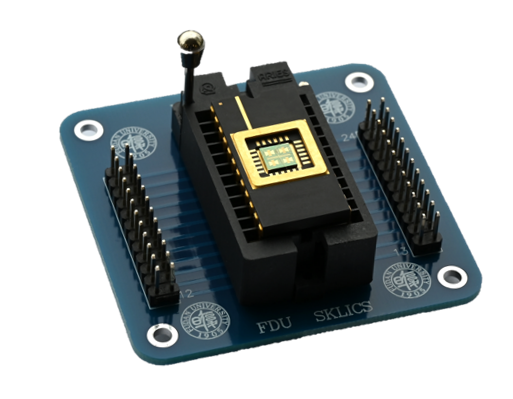

封裝后的二維-硅基混合架構(gòu)閃存芯片(帶PCB板)

這一突破攻克了

新型二維信息器件工程化的關(guān)鍵難題

為新一代顛覆性器件縮短應(yīng)用化周期提供范例

也為推動信息技術(shù)邁入全新高速時代

提供強力支撐

相關(guān)研究成果以

《全功能二維-硅基混合架構(gòu)閃存芯片》

(A full-featured 2D flash chip enabled by system integration)為題

于北京時間10月8日晚間

在《自然》(Nature)期刊上發(fā)表

從原子級器件到功能芯片

跨越“從實驗室到工廠”鴻溝

大數(shù)據(jù)與人工智能時代對數(shù)據(jù)存取性能提出了極致要求,而傳統(tǒng)存儲器的速度與功耗已成為阻礙算力發(fā)展的“卡脖子”問題之一。今年4月,周鵬-劉春森團隊于《自然》(Nature)期刊提出“破曉”二維閃存原型器件,實現(xiàn)了400皮秒超高速非易失存儲,是迄今最快的半導(dǎo)體電荷存儲技術(shù),為打破算力發(fā)展困境提供了底層原理。

“破曉(PoX)”皮秒閃存器件

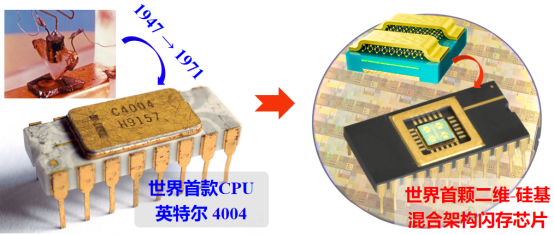

然而,顛覆性器件要真正走向系統(tǒng)級應(yīng)用,往往是一場漫長的馬拉松。回溯硅基芯片的發(fā)展歷程,半導(dǎo)體晶體管自1947年誕生起,歷經(jīng)貝爾實驗室、仙童與英特爾等頂尖力量二十余年的接力研發(fā),才終于催生出全球第一顆CPU。

作為集成電路的前沿領(lǐng)域,二維電子學(xué)在近年來獲得諸多關(guān)注,但研究者們最關(guān)心的問題莫過于“LAB to FAB(從實驗室到工廠)”難題,也就是這項技術(shù)未來是否可以得到真正的應(yīng)用。如何加速產(chǎn)業(yè)化進程,讓二維電子器件走向功能芯片?周鵬-劉春森團隊主動融入產(chǎn)業(yè)鏈,嘗試從未來應(yīng)用的終點出發(fā),“從10到0”倒推最具可能性的技術(shù)發(fā)展路徑。

“從目前技術(shù)來看,存儲器是二維電子器件最有可能首個產(chǎn)業(yè)化的器件類型。因為它對材料質(zhì)量和工藝制造沒有提出更高要求,而且能夠達(dá)到的性能指標(biāo)遠(yuǎn)超現(xiàn)在的產(chǎn)業(yè)化技術(shù),可能會產(chǎn)生一些顛覆性的應(yīng)用場景。”在存儲器領(lǐng)域深耕多年的周鵬認(rèn)為。

當(dāng)前,CMOS(Complementary Metal Oxide Semiconductor,互補金屬氧化半導(dǎo)體)技術(shù)是集成電路制造的主流工藝,市場中的大部分集成電路芯片均使用CMOS技術(shù)制造,產(chǎn)業(yè)鏈較為成熟。團隊認(rèn)為,如果要加快新技術(shù)孵化,就要將二維超快閃存器件充分融入CMOS傳統(tǒng)半導(dǎo)體產(chǎn)線,而這也能為CMOS技術(shù)帶來全新突破。

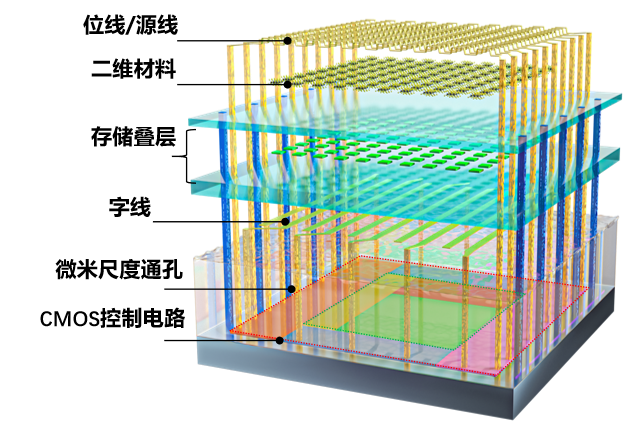

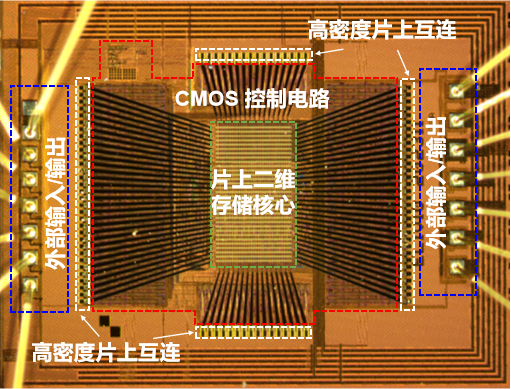

二維-硅基混合架構(gòu)閃存芯片結(jié)構(gòu)示意圖,包含二維模塊、CMOS控制電路和微米尺度通孔

基于CMOS電路控制二維存儲核心的全片測試支持8-bit指令操作,32-bit高速并行操作與隨機尋址,良率高達(dá)94.3%。這也是迄今為止世界上首個二維-硅基混合架構(gòu)閃存芯片,性能“碾壓”目前的Flash閃存技術(shù),首次實現(xiàn)了混合架構(gòu)的工程化。

“從第一個原型晶體管到第一款 CPU花了大約24年,而我們通過把先進技術(shù)融入工業(yè)界現(xiàn)有的CMOS產(chǎn)線,這一原本需要數(shù)十年的積累過程被大幅壓縮,未來可以進一步加速探索顛覆性應(yīng)用。”劉春森總結(jié)。

世界首顆二維-硅基混合架構(gòu)閃存芯片。左側(cè)為半導(dǎo)體晶體管從原型器件到第一款CPU。右側(cè)為二維閃存器件結(jié)構(gòu)、8英寸流片CMOS晶圓、二維-硅基混合架構(gòu)閃存芯片。

創(chuàng)新集成工藝

實現(xiàn)二維材料與CMOS融合

為了找到這條“正確的路”,團隊前期經(jīng)歷了5年的探索試錯,在單個器件、集成工藝等多點協(xié)同攻關(guān)。團隊的第一項集成工作發(fā)表于2024年的Nature Electronics,在最理想的原生襯底上實現(xiàn)了二維良率的突破,這為他們在真實復(fù)雜的CMOS襯底上解決問題提供了基礎(chǔ)。

2024年 Nature Electronics

人們現(xiàn)在所說的芯片多由硅材料制作。而硅材料和二維材料可以說天差地別——硅片厚度往往在幾百微米,一些薄層硅至少也有幾十納米;而二維半導(dǎo)體材料是原子級別,相當(dāng)于厚度不到1納米。

“二維半導(dǎo)體作為一種全新的材料體系,在國際上所有的集成電路制造工廠里都是不存在的。一旦引入新材料,就有可能對其他電子器件產(chǎn)生不可估量的影響,導(dǎo)致產(chǎn)線被污染,這是所有芯片廠商都無法接受的。”周鵬介紹。

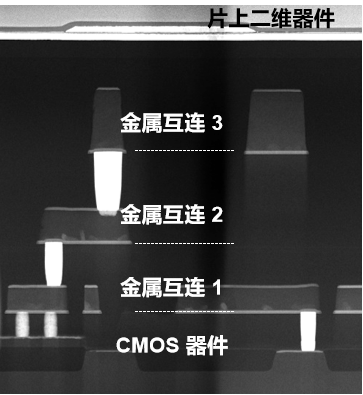

如何將二維材料與CMOS集成又不破壞其性能,是團隊需要攻克的核心難題。CMOS電路表面有很多元件,如同一個微縮“城市”,有高樓也有平地,高低起伏;而二維半導(dǎo)體材料厚度僅有1-3個原子,如同“蟬翼”般纖薄而脆弱,如果直接將二維材料鋪在CMOS電路上,材料很容易破裂,更不用談實現(xiàn)電路性能。

“就好比我們從太空看上海,似乎很平坦,但這個城市內(nèi)部其實有400多米、100多米或者幾十米高度不等的建筑。如果鋪一張薄膜在城市上方,膜本身就會不平整。”周鵬形象比喻道。

這也是為什么全世界的二維半導(dǎo)體研究者目前只能在極為平整的原生襯底上加工材料。一種解決思路是將CMOS的襯底“磨平”以適應(yīng)二維材料,但要實現(xiàn)原子級平整并不現(xiàn)實。

二維-硅基混合架構(gòu)閃存芯片光學(xué)顯微鏡照片

“我們沒有必要去改變CMOS,而需要去適應(yīng)它。”團隊決定從本身就具有一定柔性的二維材料入手,通過模塊化的集成方案,先將二維存儲電路與成熟CMOS電路分離制造,再與CMOS控制電路通過高密度單片互連技術(shù)(微米尺度通孔)實現(xiàn)完整芯片集成。

二維-硅基混合架構(gòu)閃存芯片透射電子顯微鏡照片

正是這項核心工藝的創(chuàng)新,實現(xiàn)了在原子尺度上讓二維材料和CMOS襯底的緊密貼合,最終實現(xiàn)超過94%的芯片良率。團隊進一步提出了跨平臺系統(tǒng)設(shè)計方法論,包含二維-CMOS電路協(xié)同設(shè)計、二維-CMOS跨平臺接口設(shè)計等,并將這一系統(tǒng)集成框架命名為“長纓(CY-01)架構(gòu)”。

計劃3-5年集成至百萬量級

有望顛覆傳統(tǒng)存儲器體系

銜接起實驗室成果與產(chǎn)業(yè)化需求,確保理論創(chuàng)新與應(yīng)用轉(zhuǎn)化能夠“雙腿并行”,是周鵬-劉春森團隊在研究中相互交織的兩條主線。依托前期完成的研究成果與集成工作,此次打造出的芯片已成功流片。

從基礎(chǔ)研究到工程化應(yīng)用,團隊已跨越最艱難一步,后續(xù)迭代進程將進一步加快。他們下一步計劃建立實驗基地,與相關(guān)機構(gòu)合作,建立自主主導(dǎo)的工程化項目,并計劃用3-5年時間將項目集成到兆量級水平,期間產(chǎn)生的知識產(chǎn)權(quán)和IP可授權(quán)給合作企業(yè)。

人工智能時代,當(dāng)下的AI系統(tǒng)瓶頸正在從前端的算力轉(zhuǎn)向后端的存儲和數(shù)據(jù),未來的模型會越來越龐大。多位業(yè)界人士表示看好該成果以更快速度從實驗室走向大規(guī)模應(yīng)用,融入個人電腦、移動端設(shè)備等場景。

存儲器產(chǎn)業(yè)界代表認(rèn)為,團隊研發(fā)的二維器件具有天然的訪問速度優(yōu)勢,可突破閃存本身速度、功耗、集成度的平衡,未來或可在3D應(yīng)用層面帶來更大的市場機會,下一步期待通過產(chǎn)學(xué)研協(xié)同合作,為每年600億美金的市場帶來變革。

“這項成果不只是延續(xù)性的技術(shù)改良,更多的是存儲速度和效率上的一次顛覆性進步。”復(fù)容投資代表分析,該技術(shù)已形成“科學(xué)-工程-系統(tǒng)”閉環(huán),符合AI時代算力存儲需求,且通過依托成熟CMOS產(chǎn)線,能夠縮短研發(fā)周期,降低商業(yè)化門檻。

“這是中國集成電路領(lǐng)域的‘源技術(shù)’,使我國在下一代存儲核心技術(shù)領(lǐng)域掌握了主動權(quán)。”展望二維-硅基混合架構(gòu)閃存芯片的未來,周鵬-劉春森團隊期待該技術(shù)顛覆傳統(tǒng)存儲器體系,讓通用型存儲器取代多級分層存儲架構(gòu),為人工智能、大數(shù)據(jù)等前沿領(lǐng)域提供更高速、更低能耗的數(shù)據(jù)支撐,讓二維閃存成為AI時代的標(biāo)準(zhǔn)存儲方案。

周鵬-劉春森團隊

復(fù)旦大學(xué)集成電路與微納電子創(chuàng)新學(xué)院、集成芯片與系統(tǒng)全國重點實驗室研究員劉春森和教授周鵬為論文通訊作者,劉春森研究員和博士生江勇波、沈伯僉、袁晟超、曹振遠(yuǎn)為論文第一作者。研究工作得到了科技部、教育部、國家自然科學(xué)基金委、上海市科委、科學(xué)探索獎等項目的資助,以及教育部創(chuàng)新平臺的支持。

論文鏈接:

https://www.nature.com/articles/s41586-025-09621-8