優化放大器電路中的輸入和輸出瞬態穩定時間

關鍵詞: 放大器電路 瞬態穩定時間 Riso+DFB電路 反饋比優化 運算放大器

優化放大器電路中的輸入和輸出瞬態穩定時間

運算放大器電路通常在執行系統功能時需要響應輸入和輸出瞬態。部分電路主要設計用于接受不同的輸入瞬態,如傳感器信號調節電路;而其他電路則提供輸出瞬態,例如模數轉換器 (ADC)輸入或基準驅動器。在運算放大器電路設計中,同一電路的輸出(負載)階躍與輸入階躍的輸出穩定響應時間的差異經常被忽視。

在大多數電路中,輸出負載直接連接到運算放大器的輸出端;響應時間在很大程度上基于運算放大器對所需負載瞬態及后續恢復提供支持的能力。然而,該行為取決于電路拓撲。在運算放大器輸出電壓 (Vopa)不直接連接到負載的電路中,輸出穩定響應會與輸入響應大不相同。在放大器必須驅動容性負載 (Cload)的情況下,此類電路的一個常見示例是具有雙反饋 (Riso+DFB) 電路拓撲的隔離電阻器。在 Vopa 和 Cload 網絡之間使用隔離電阻器 (Riso)并存在從反饋電容器 (Cf)和反饋電阻器 (Rf)返回反相輸入 (IN-)的兩個反饋路徑,此電路也因此得名。

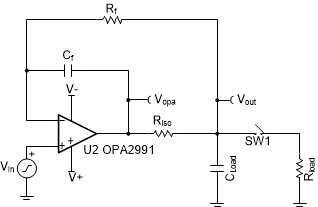

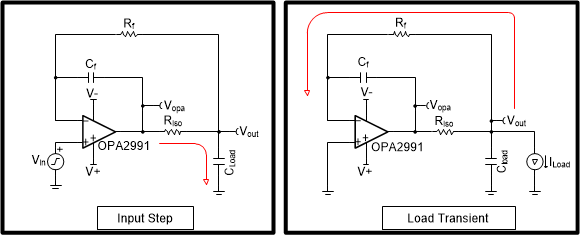

圖 1-1 顯示了一個用于驅動容性負載 (Cload) 的 Riso+DFB 電路示例。輸入端直接連接到電壓源,因此運算放大器必須對輸入端發生的變化做出反應。在含有一個簡單的開關 (SW1) 和電阻負載 (Rload) 的基本情況下,放大器電路必須對輸出端出現的負載瞬態做出響應。

圖 1-1 具有雙反饋的 Riso原理圖

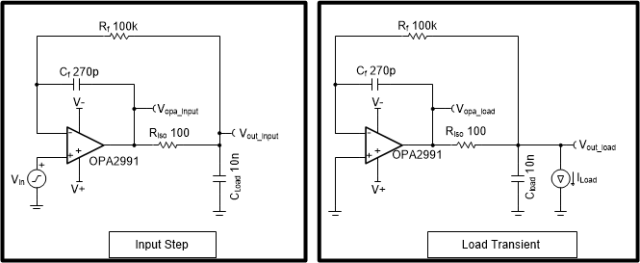

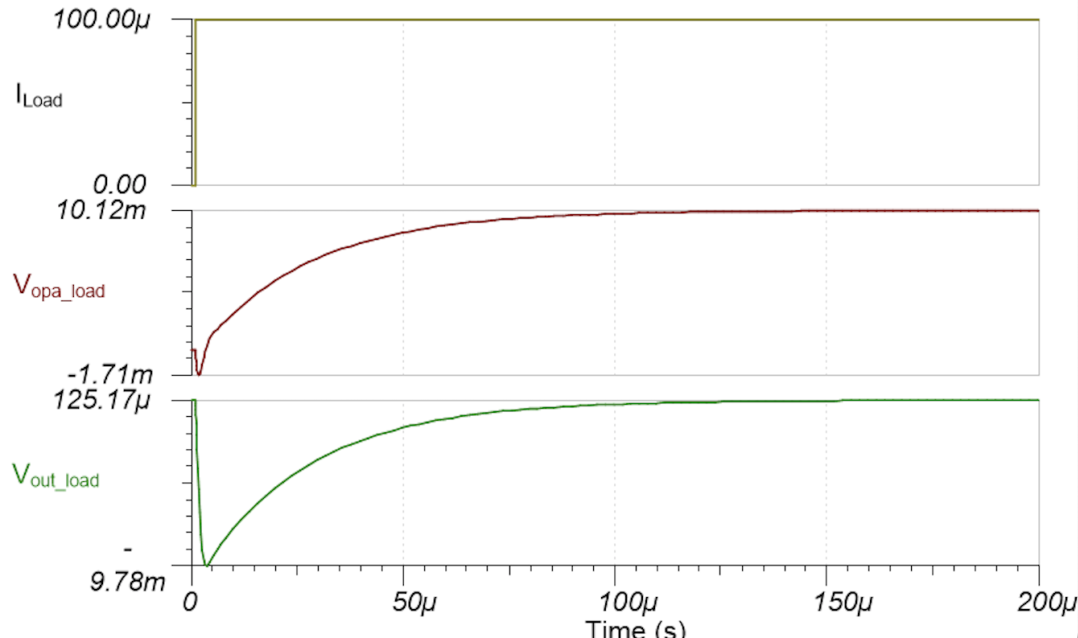

圖 1-2 中的兩個仿真電路展示了輸入階躍和負載瞬態輸出響應之間的差異。圖 1-2(a) 將輸入電壓階躍應用于電路的輸入端,而 圖 1-2(b) 將負載電流階躍應用于輸出端。在負載瞬態電路中,通過將流經Riso (Iload x Riso)的負載電流 (Iload)形成的輸出壓降設置為與輸入階躍幅度相等,將兩個電路中 Vopa 的初始變化設置為10mV,從而實現同級比較。10mV 的輸出階躍幅度可防止運算放大器出現大信號趨穩行為,例如壓擺率限制。此外,輸出電流必須足夠小,以防止運算放大器進入大信號短路電流限制范圍。

圖 1-2 輸入階躍 (a) 和負載瞬態 (b) 仿真電路

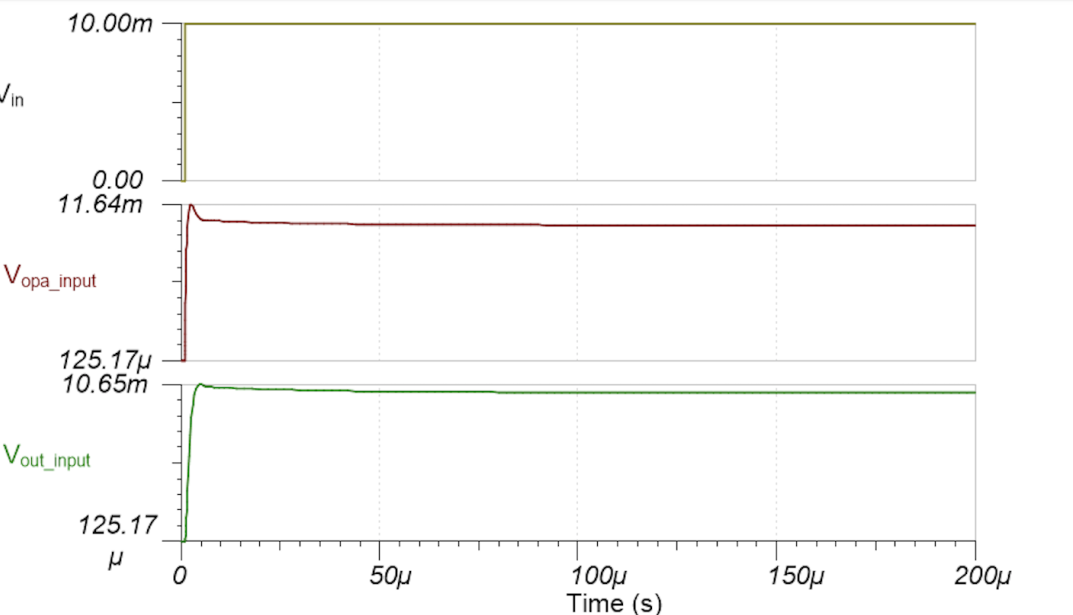

圖 1-3 顯示了兩個仿真電路的結果。按照設計,針對輸入和輸出響應,Vopa 的初始變化均為 10mV。但是負載輸出電壓 (Vout) 穩定所需的時間在兩個電路之間是不同的;輸入階躍電路的趨穩速度比輸出負載瞬態階躍電路快得多。例如,若要穩定到 0.05%(相當于 10 位),輸入階躍電路需要 5.02μs,輸出負載瞬態電路需要 189.42μs。

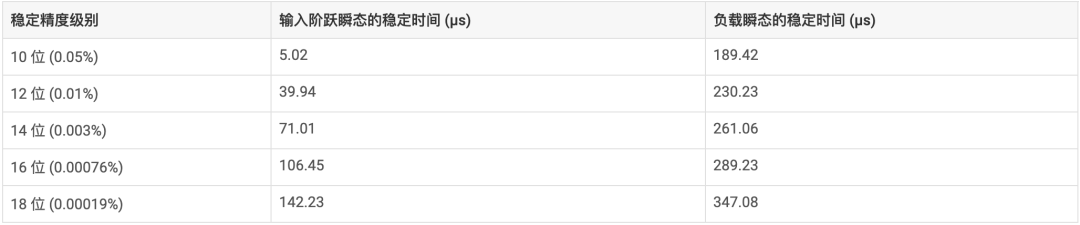

表 1-1 列出了圖 1-2 中輸入階躍電路和負載瞬態階躍電路要實現10 至 18 位分辨率采集系統所需的輸出穩定時間之間的差異。由于不同的輸出阻抗和開環增益曲線會造成更加細微的影響,測試備選運算放大器將獲得不同的穩定響應。

表 1-1 不同穩定精度水平的輸入和輸出瞬態穩定時間

圖 1-3 輸入階躍 (a) 和輸出負載瞬態 (b) 電路的

輸出穩定響應

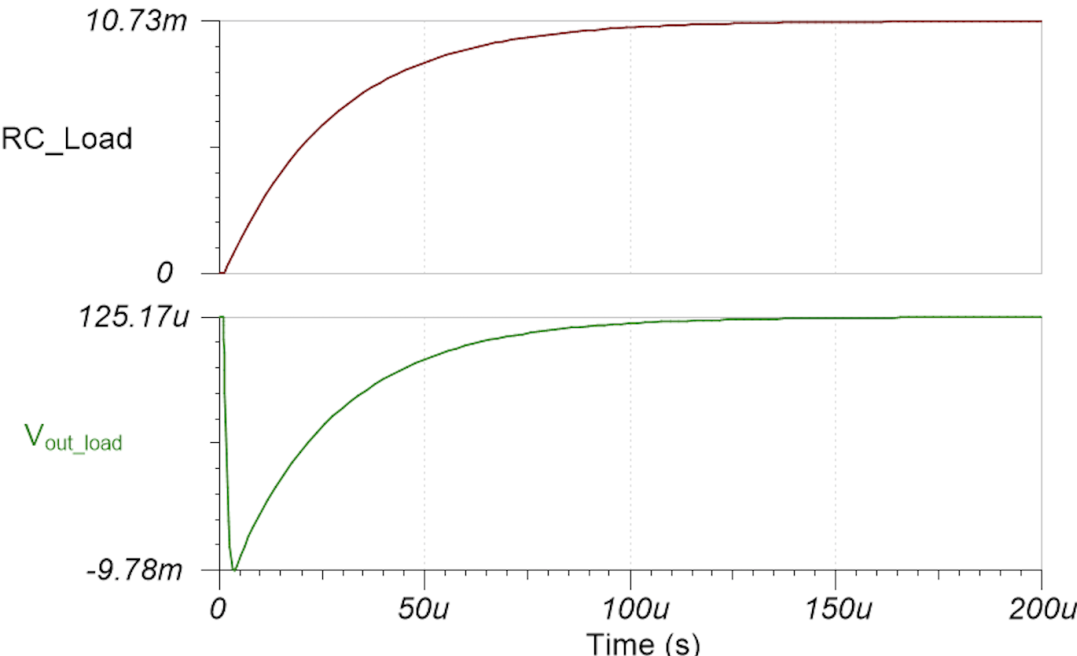

圖 1-4 顯示了對輸入和輸出瞬態的輸出穩定響應起主導作用的元件,如紅色箭頭所示。對于輸入階躍瞬態,Riso和 Cload電阻-電容 (RC) 時間常數決定了輸出穩定時間。發生輸入階躍時,Vopa立即響應輸入電壓階躍。隨著運算放大器輸出電壓升高,Vout會因 Riso和 Cload而出現延遲。

對于負載瞬態,Rf 和 Cf RC 時間常數決定了輸出穩定響應。發生負載瞬態時,Vout立即下降10mV (Risox Iload)。Vopa響應 Vout下降所需的時間取決于 Rf和 Cf產生的 RC 延時時間。

圖 1-4 主導輸入階躍 (a) 和輸出負載 (b) 瞬態響應的

RC 時間常數

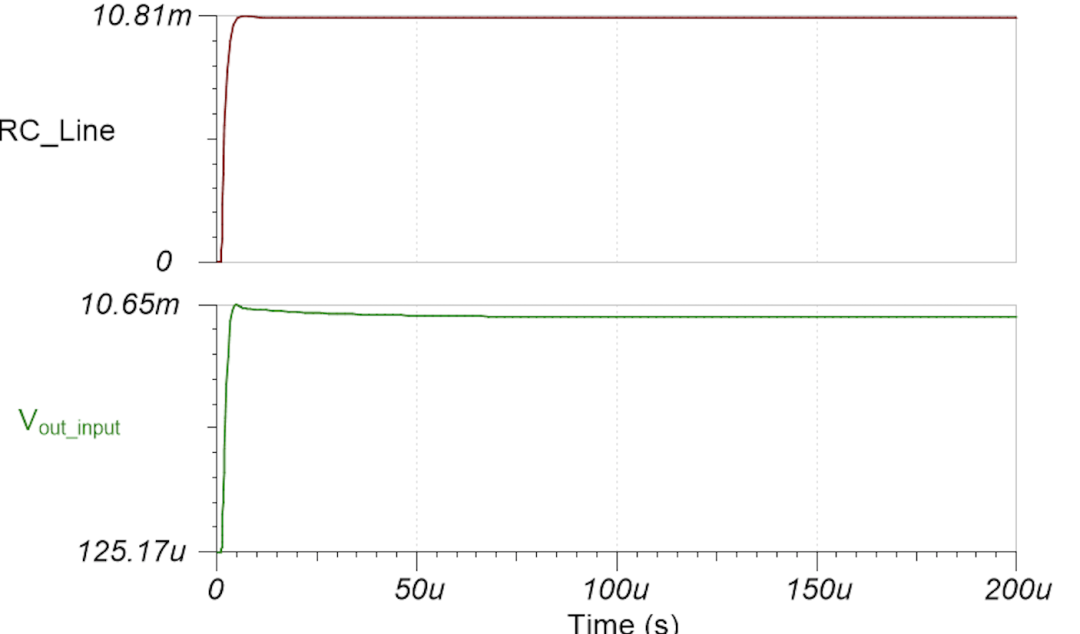

圖 1-5 將輸入階躍和負載瞬態輸出穩定時間(底部響應)與前文所述的起主導作用的RC 時間常數(頂部響應)進行了比較。圖 1-5F(a) 將 Vout的輸入階躍穩定時間與具有100Ω電阻器和10nF電容器(Riso和 Cload)的 RC 電路響應進行了比較。圖 1-5(b) 將輸出瞬態穩定時間與具有100kΩ電阻器和270pF電容器(Rf和 Cf)的 RC 電路響應進行了比較。RC 電路上升時間與輸入階躍和負載瞬態輸出穩定響應一致,從而證實了上述理論。

圖 1-5 輸入階躍 (a) 和輸出負載 (b) 瞬態穩定時間

(RC 時間常數起主導作用)

下文將討論Riso+DFB 電路的穩定性標準,并介紹如何優化反饋比,以獲得更好的負載瞬態穩定時間。首先,運算放大器作為單位增益緩沖器,必須穩定驅動 Riso+Cload組合。其次,由 Rf和 Cf形成的 1/Beta 極點必須至少小于來自 Riso 和 Cload 的零點頻率的一半。

·單位增益緩沖器驅動 Risox Cload的相位裕度:>45°

·反饋比:(Rfx Cf)/(Risox Cload) > 2

雖然穩定運行的反饋路徑的最小比率為2,但穩定電路沒有最大比率。只要滿足第一個標準,反饋路徑比率可穩定保持在 10、100 甚至 1,000,并具有類似的相位裕度結果。然而,如 圖 1-5 所示,輸出負載響應基于由 Rf和 Cf元件形成的時間常數。因此,雖然穩定,但較大的比率將導致負載響應比輸入響應慢得多。

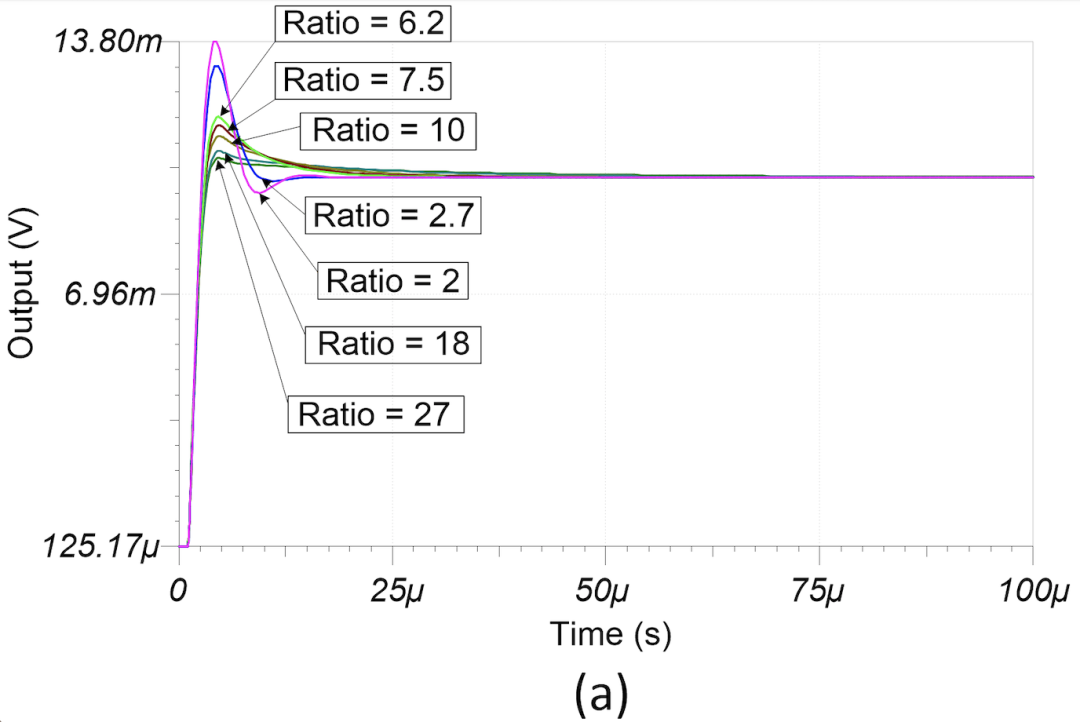

圖 1-6 顯示了輸出穩定響應如何隨改變(Rfx Cf)/(Risox Cload)的比率而化變。當反饋比接近最小標準 2 時,輸入階躍和輸出負載瞬態的輸出響應幾乎相等,但會增加一些過沖和振鈴。增加 (Rfx Cf)/(Risox Cload) 的比率會產生更大的阻尼輸出,一旦比率大于 20,該輸出對輸入階躍響應的影響最小。然而,該比率對Rfx Cf時間常數起主導作用,因此較大的比率會繼續增加負載瞬態輸出響應時間。

圖 1-6 輸入階躍(頂部)和輸出負載(底部)瞬態的

多個比率的輸出穩定響應

因此,為了在響應輸出負載瞬態時實現卓越性能,應在設計電路時采用接近 2 的 (Rfx Cf)/(Risox Cload) 比率。由于運算放大器特性與電路元件和多樣性之間的相互作用將導致某些組合低于目標比率,更保守的設計方法將此比率設置在4 和 10 之間。反饋元件比率低于 2 將影響電路的穩定性。

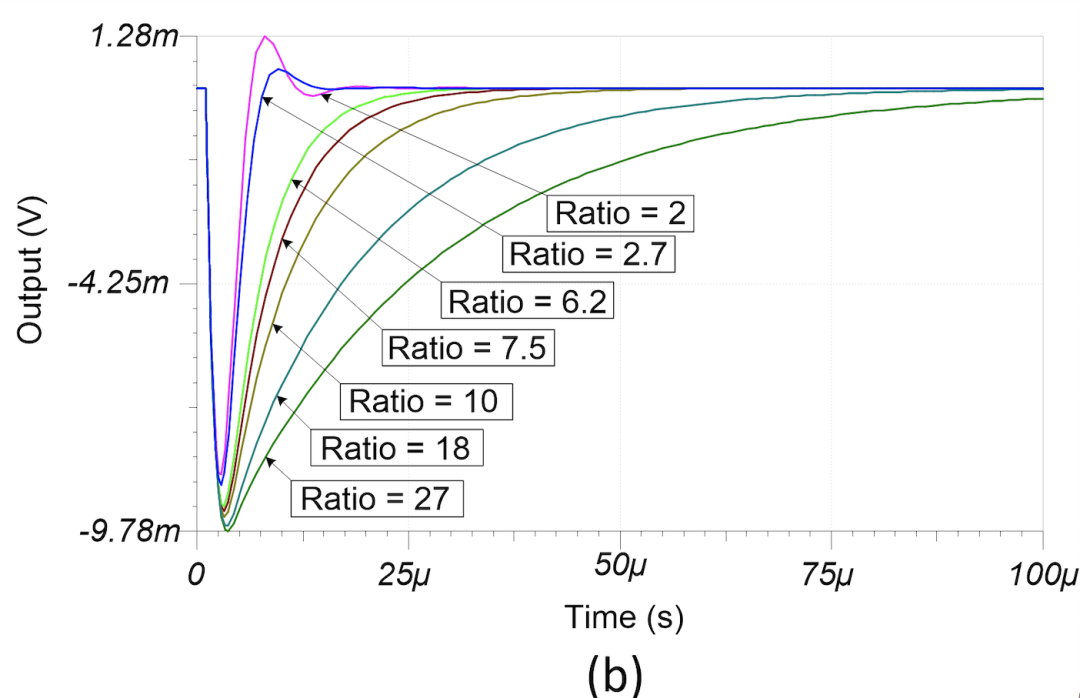

這種效應發揮作用的一個實際例子是 ADC 基準驅動電路,如圖 1-7 所示。

圖 1-7 ADC 基準驅動電路

在 ADC 的轉換階段,逐次逼近過程中會將內部電容器數模轉換器 (CDAC)組切換到電路中。每次新的電容器切換到電路中時,外部驅動電路所需的電流突發將作為負載瞬態出現。因此,如果沒有正確配置電路反饋比,Riso+DFB 電路可能無法正確穩定至負載響應。

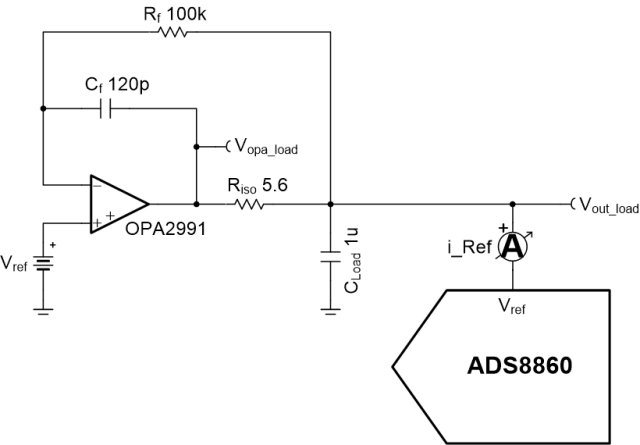

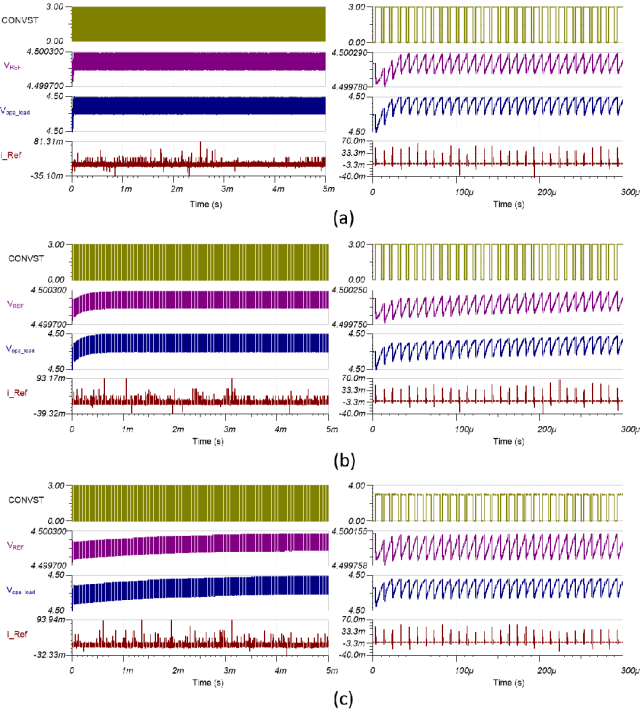

圖 1-8 顯示了電路仿真中的上述效應,其中使用 圖 1-7 中的運算放大器電路作為ADS8860的基準緩沖器,ADS8860 是一個16 位逐次逼近寄存器 ADC,在本示例中配置為以 100kSPS 的速率進行采樣。將電路中的反饋路徑比值從大約3.6變化到360顯示了負載穩定時間的差異。正如圖 1-5 中的結果所預期,具有較高比率的電路需要更長的時間使基準緩沖器電路達到平衡,從而導致轉換之間的最低有效位穩定誤差小于 1/2。

最低模擬比率 – 圖 1-8(a) 中的 3.6 – 需要大約四個樣本達到平衡,而圖 1-8(c) 中比率為 360,需要超過 400 個樣本(或大約 4ms)電路才能達到平衡,這很好地說明這一點。應用通常采用間歇性的樣本突發,對于具有圖 1-8(c) 所示結果的電路可能不會在樣本突發完成之前完全達到平衡。不穩定的基準會導致出現轉換錯誤和 AC 性能下降。如前所述,比率為 3.6 和 360 的電路的相位裕度和輸入響應幾乎相同;如果您沒有正確設計電路并驗證輸出負載響應,則可能會出現意外的電路結果。

圖 1-8 不同反饋比率的 ADC 基準驅動趨穩:

3.6 (a);36 (b);和 360 (c)。左圖和右圖分別顯示了

5ms 時間標度和 300μs 時間標度,結果相同。

結論

包括 ADC 輸入和 ADC 基準電壓驅動器在內的應用需要使用運算放大器電路對輸出負載瞬態和輸入階躍瞬態進行響應。這些應用中經常使用的 Riso+DFB 電路拓撲在輸出和輸入階躍的輸出穩定響應時間上會存在很大差異,具體取決于所選的電路值和比率。如果用戶在設計這些電路時僅使用輸入階躍進行電路分析,則輸出負載穩定可能會出現意外結果,從而對應用產生負面影響。因此,在設計電路時,必須同時響應輸入階躍瞬態和輸出負載瞬態。驗證對兩種瞬態類型的穩定響應是否滿足電路穩定要求,這不失為一個好方法。

網址:www.baitaishengshi.com